### DOCUMENTO COMPLEMENTARIO AL INFORME "SITUACIÓN Y TENDENCIAS EN EL USO DE LA IA EN EL SECTOR DE LA DEFENSA"

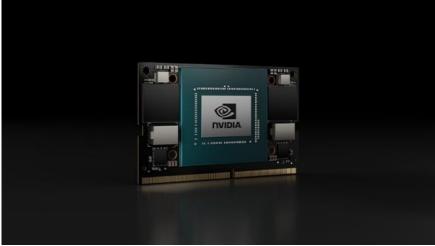

## Hardware/Chips para inteligencia artificial aplicada a la defensa y seguridad

### José María Insenser

Miembro del Foro de Empresas Innovadoras (FEI)

AMETIC (IPCEI Chip)

### Tabla de contenido

| Introducción                                                                | 3  |

|-----------------------------------------------------------------------------|----|

| Objetivos                                                                   | 5  |

| IA/Tecnología semiconductores                                               | 5  |

| Círculo virtuoso IA/Tecnología de semiconductores                           | 5  |

| Uso dual de los semiconductores                                             | 6  |

| Impulsores actuales de la industria de semiconductores                      | 8  |

| Evolución de la Tecnologías de Semiconductores                              | 9  |

| Ley de Moore                                                                | 9  |

| Concepto de Nodo Tecnológico y su evolución                                 | 11 |

| Hoja de ruta IRDS                                                           | 15 |

| "More Moore"                                                                | 16 |

| "More than Moore"                                                           | 17 |

| "Beyond CMOS"                                                               | 18 |

| SoC y SiP                                                                   | 19 |

| Chips para aplicaciones en Defensa                                          | 23 |

| Materiales para la fabricación de chips para la defensa                     | 24 |

| Diseño de chips para la defensa                                             | 30 |

| Sistemas Integrados                                                         | 30 |

| Sensores en la Defensa                                                      | 31 |

| Semiconductores y su uso en Defensa                                         | 32 |

| Condiciones que deben cumplir los chips de Defensa                          | 32 |

| Hardware Abierto (RISC V)                                                   | 34 |

| Procesos Tecnológicos para Defensa                                          | 35 |

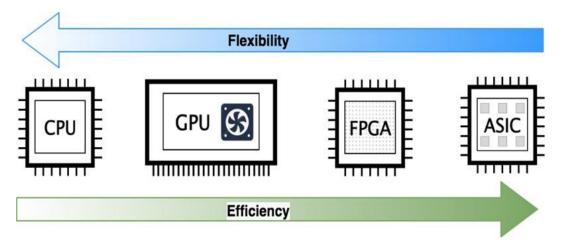

| Tipos de chips para su uso en IA                                            | 37 |

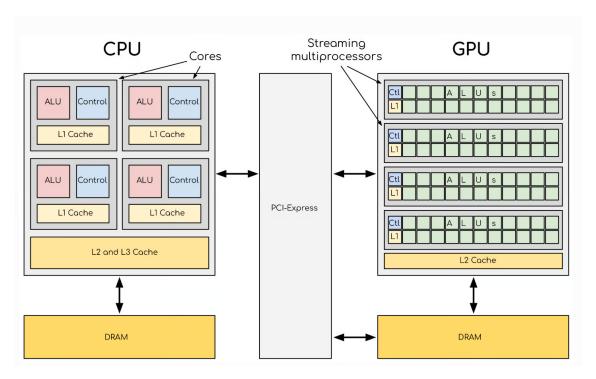

| Comparación entre Arquitecturas Von Neuman (CPUs) y Paralelas (GPUs,ASICS)  | 39 |

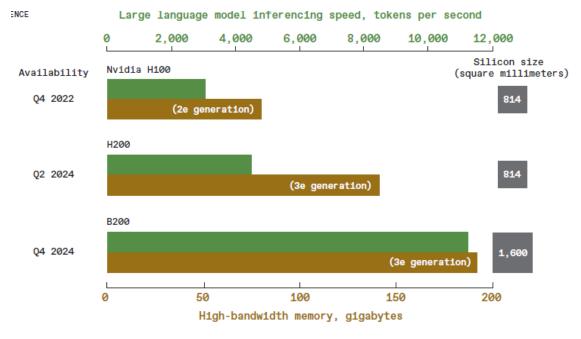

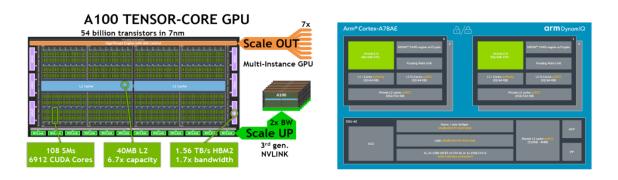

| GPUs: Tipos, Prestaciones. NVIDIA H100 Tensor Core.                         | 41 |

| FPGAs: Xilinx VITIS (AMD)                                                   | 46 |

| ASICS: Chips dedicados.                                                     | 50 |

| DNN                                                                         | 50 |

| CHIPS NEUROMÓRFICOS                                                         | 51 |

| AIMC (Analog-In-Memory-Computing)                                           | 58 |

| Aceleradores IA (ASICs): CEREBRAS, SambaNova, TPU GOOGLE, CAMBRICON (China) | 60 |

| CEREBRAS                                                                    | 61 |

| Sambanova                                                                                                         | 64              |

|-------------------------------------------------------------------------------------------------------------------|-----------------|

| GROQ                                                                                                              | 66              |

| GOOGLE TPU                                                                                                        | 67              |

| CAMBRICON (China)                                                                                                 | 69              |

| Principales Aplicaciones de chips IA en el borde. ASICs aceleradores de IA en el b                                | <b>orde.</b> 70 |

| Chips IA para su uso en Defensa: Proyectos de chips IA para Defensa financiados Agencias (DARPA, EDF, ESA, NASA). | •               |

| Evolución y tendencias de Chips IA:                                                                               | 74              |

| Detección neuromórfica                                                                                            |                 |

| Fotónica Integrada                                                                                                | 80              |

| Microelectrónica para computación cuántica                                                                        | 82              |

| Ejemplos de uso avanzado de chips para IA en Defensa                                                              | 85              |

| Chips para cifrado Inteligente                                                                                    | 85              |

| Chips para IoT militar                                                                                            | 88              |

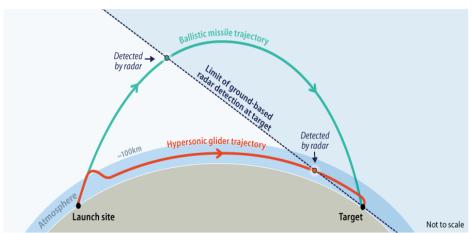

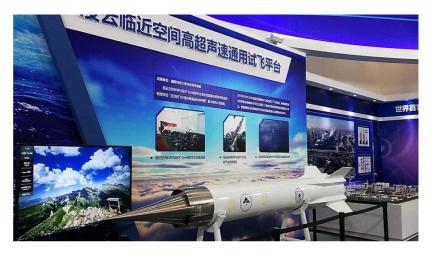

| Chips para guiado de misiles hipersónicos                                                                         | 89              |

| Chips para enjambre de drones                                                                                     | 91              |

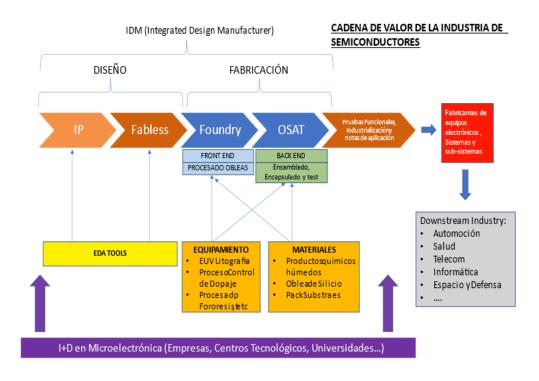

| Modelo de negocio de los semiconductores                                                                          | 93              |

| Cadena de Valor de los Semiconductores                                                                            | 93              |

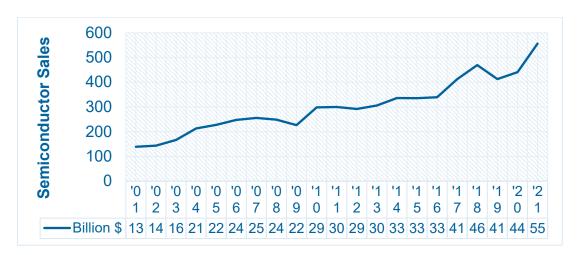

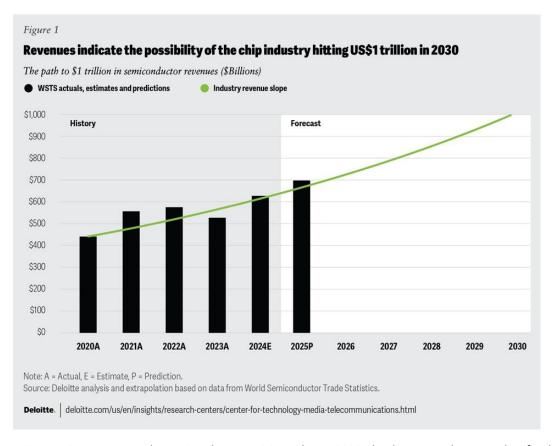

| Mercado de los Semiconductores                                                                                    | 97              |

| Crecimiento previsto del mercado de semiconductores en la década (hasta 202 sectores verticales                   |                 |

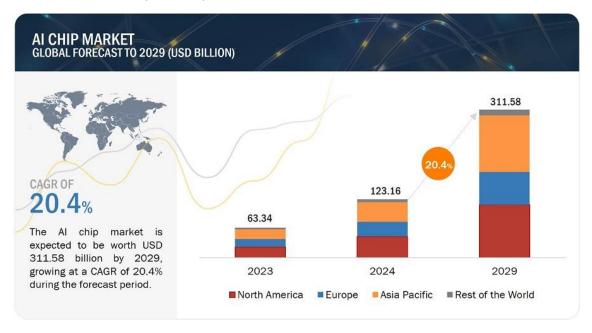

| Mercado de los chips para IA                                                                                      | 103             |

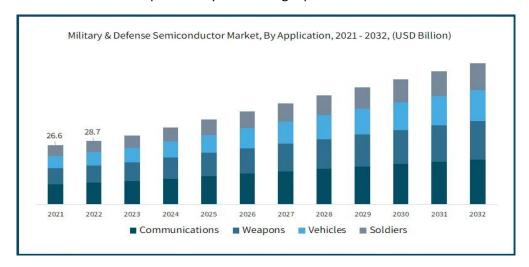

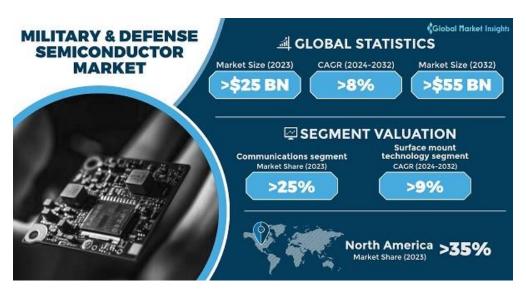

| Mercado de los Semiconductores para la Defensa                                                                    | 104             |

| Ventas de semiconductores por compañías y segmentos cadena de valor                                               | 106             |

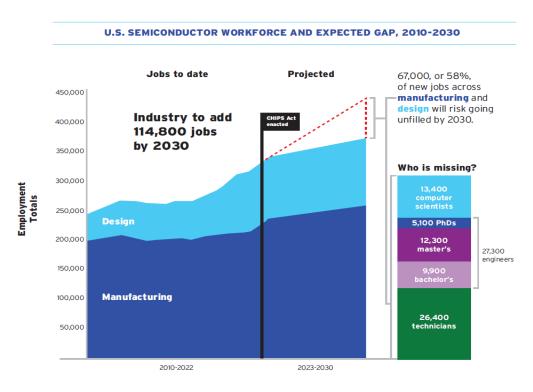

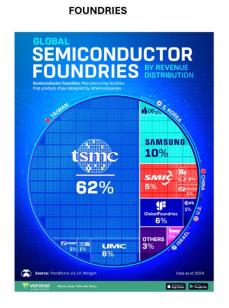

| Foundries                                                                                                         | 107             |

| Compañías Fabless                                                                                                 | 108             |

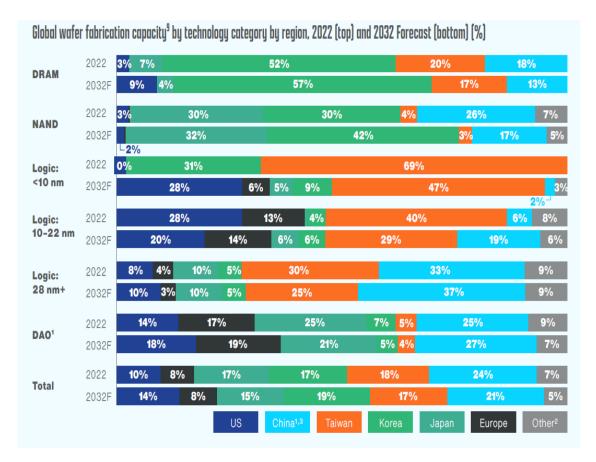

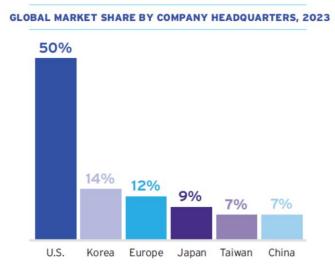

| Geopolítica y semiconductores                                                                                     | 109             |

| Situación de dependencia de Europa con EEUU en chips para IA                                                      | 109             |

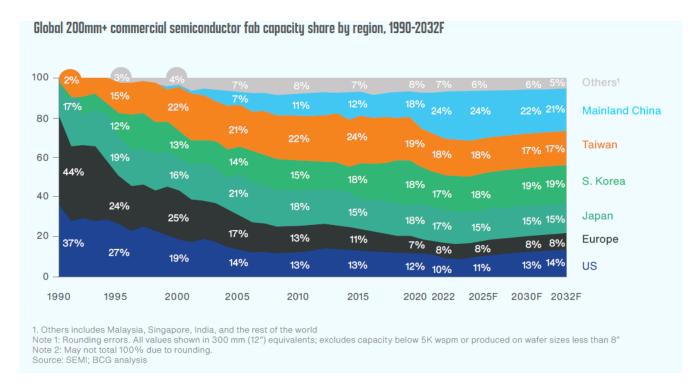

| La dependencia de fabricación de Taiwán y Corea                                                                   | 110             |

| Estado de las foundries en Europa                                                                                 | 111             |

| Control de acceso a las tecnologías                                                                               | 112             |

| Política de sanciones y contra sanciones                                                                          | 115             |

| Conclusiones                                                                                                      | 117             |

| Recomendaciones                                                                                                   | 117             |

| Ribliografía                                                                                                      | 119             |

### Introducción

La microelectrónica es, desde su aparición en la década de los 50 del siglo pasado, con la invención del circuito integrado¹, una tecnología habilitadora clave que ha posibilitado el avance de otras tecnologías que han transformado la economía y la sociedad, como la industria 4.0, las telecomunicaciones, la automoción/movilidad, las ciudades inteligentes, la aeronáutica, el sector espacial, la energía, la instrumentación, la defensa y la seguridad, la industria agroalimentaria, el Control de tráfico, la Monitorización de infraestructuras, la ciberseguridad, etc. y , por supuesto, la Inteligencia Artificial.

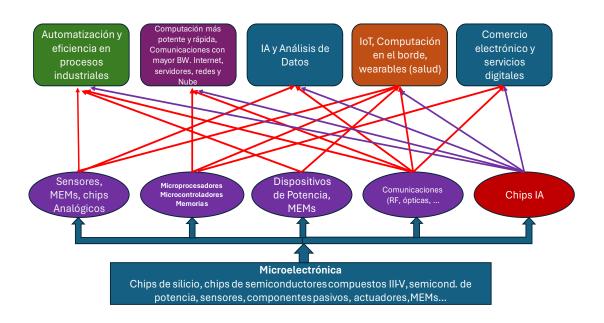

La microelectrónica está en la base de todos los procesos de digitalización y automatización industriales clave, contribuyendo de forma notable al aumento de la productividad (véase *Figura* 1).

<u>Figura 1</u>. La microelectrónica y los semiconductores son la base para el aumento de la productividad en los distintos procesos de digitalización y automatización industriales. Fuente: elaboración propia

En efecto, las **TIC (Tecnologías de la Información y las Comunicaciones)** cuyo principal substrato hardware es la microelectrónica, han contribuido desde la invención de los microprocesadores por parte de *Federico Faggin* en Intel, a principio de la década de los 70 del siglo pasado, a mejorar la productividad de las empresas que las han usado. La contribución de las TIC y los semiconductores al incremento de productividad de las empresas ha conducido, en los países donde se han implantado suficientemente las TIC en el tejido productivo, a un incremento de la Productividad Total de los Factores (PTF)<sup>2</sup> y, en consecuencia, a un crecimiento de su PIB.

SEPTIEMBRE 2025

<sup>&</sup>lt;sup>1</sup> El circuito integrado, entendido como la interconexión monolítica de dispositivos activos (transistores), fue desarrollado a finales de la década de 1950 por Bob Noyce en Fairchild y Jack Kilby en Texas Instrumens. Este último fue galardonado con el premio Nobel de Física en 2.000. Desafortunadamente Bob Noyce falleció antes.

<sup>&</sup>lt;sup>2</sup> La productividad, ya sea a nivel macroeconómico o de las empresas, puede mejorarse a través de tres canales principales: a) Aumentando **el stock de capital** mediante la inversión en maguinaria y equipo, lo

En este informe nos centramos en una parte específica de los dispositivos semiconductores que son los chips IA para la Defensa, la Seguridad y el Espacio. Los chips IA, junto a los algoritmos de IA que ejecutan, de forma similar a como han hecho los equipos electrónicos dotados de microprocesadores con su software correspondiente, también contribuyen a un incremento de la Productividad total de los Factores (PTF).

En qué medida afectará en los próximos diez años la generalización del uso de la IA, tanto en el campo civil como en el de la Defensa y el Espacio, a la Productividad Total de los Factores y, en definitiva, al bienestar de la sociedad, todavía hay pocos datos para sacar conclusiones, pero algunos economistas han construido modelos predictivos. Según el modelo propuesto por (Acemoglou, May 2024) los efectos de la IA sobre la productividad Total de los factores (PTF) en los próximos años no deberían ser más del 0,66 % del total, o aproximadamente un aumento del 0,064% en el crecimiento de la PTF anualmente.

El informe se estructura en las siguientes secciones: La sección dos trata de los objetivos generales del capítulo. La sección tres se refiere al refuerzo mutuo entre la IA y las tecnologías de semiconductores, así como al carácter dual de los semiconductores, y específicamente, los chips de IA, también se analizan los impulsores actuales de la industria de semiconductores. La sección cuarta da una panorámica sucinta de la evolución de las tecnologías de semiconductores centrándose en el concepto de nodo tecnológico que ha seguido la conocida como "Ley de Moore", que es una predicción tecnológica/económica, finalizando con la hoja de ruta IRDS (International Roadmap Devices and Systems).

La sección quinta introduce las características principales de los chips para la Defensa y el Espacio, haciendo hincapié en los diversos materiales semiconductores empleados, las características del diseño y el proceso tecnológico de este tipo de chips. La sección sexta se centra en los tipos de chips específicos para IA, se comentan las arquitecturas de las CPUs y GPUs, se introducen los conceptos de SoC (System on Chip) y SiP (System in Package) e integración heterogénea (Chiplets..), GPUs, FPGAs y ASICs (Chips dedicados) DNN (Redes Neuronales Profundas), chips neuromórficos, diversos chips comerciales utilizados, se aborda también como muy importante para la Defensa, los chips para computación en el borde, integración de sensores, los chips IA para su uso en Defensa (nube y borde): Proyectos de chips IA para defensa financiados por Agencias Gubernamentales (NASA, ESA, etc.), por último, en esta sección, se analizan las tendencias futuras de chips IA: Chips de computación en memoria, chips de fotónica integrada, microelectrónica para computación cuántica.

La sección séptima se centra en el modelo de negocio de los semiconductores, basándose en su cadena de valor, proporcionándose algunos datos sobre las previsiones del mercado de semiconductores en los próximos años. La sección octava propone ejemplos de uso avanzado de chips IA para la defensa, como chips para aplicaciones en enjambre de drones, para guiado de misiles hipersónicos, para IoT militar y reconocimiento de imágenes. La última sección, la novena, se centra en geopolítica y semiconductores.

que permite a los trabajadores generar una mayor producción con los mismos insumos o con menos; b) Elevando la calidad del capital humano mediante mejoras específicas en las habilidades y competencias de los empleados; y c) Aumentando la eficiencia de la interacción entre el capital y el trabajo. Esta medida se conoce como productividad total de los factores (PTF). Un aumento de la PTF refleja un mayor nivel de eficiencia en el proceso de producción, en el que se genera más producción sin un aumento proporcional de los insumos. Capta los efectos del progreso tecnológico (innovaciones) y la mejora de las prácticas de gestión.

### **Objetivos**

El Objetivo general del informe es el de analizar las tecnologías actuales y las proyecciones futuras en el diseño y fabricación de chips para la IA aplicada a la Defensa (nube y computación en el borde). También se da una panorámica general de las tecnologías de semiconductores, centrándonos en su cadena de valor y sus segmentos principales: Diseño de los chips, Fabricación de estos en el proceso tecnológico para el que se ha diseñado y encapsulado y prueba. De suma importancia es considerar que los chips IA son para aplicaciones de Defensa y del Espacio, lo que implica una serie de consideraciones en el diseño, fabricación, encapsulado y prueba de los chips, relacionados con el cumplimiento de estándares específicos para Defensa y Espacio, es decir, tienen que estar certificados para dichas aplicaciones. En cuanto a objetivos específicos, se consideran, principalmente, los siguientes:

- Analizar las características específicas de los semiconductores adaptados a las necesidades de la Defensa y del Espacio.

- Describir y analizar los requerimientos de los chips para la IA aplicada a la Defensa y al Espacio.

- Analizar la influencia de la geopolítica en la cadena de suministros para la IA aplicada a la Defensa y al Espacio.

- Extraer conclusiones que conduzcan a la elaboración de una serie de recomendaciones concretas, en particular para aumentar, en lo posible, la autonomía estratégica y alineamientos con las estrategias europeas de semiconductores e IA.

### IA/Tecnología semiconductores

### Círculo virtuoso IA/Tecnología de semiconductores.

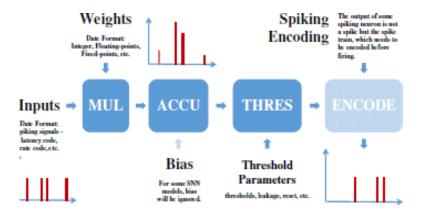

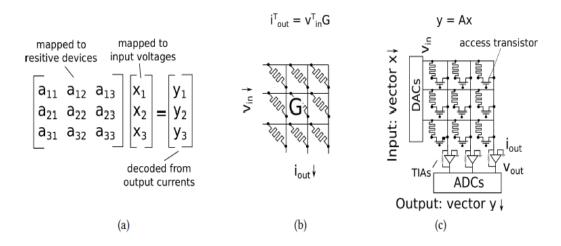

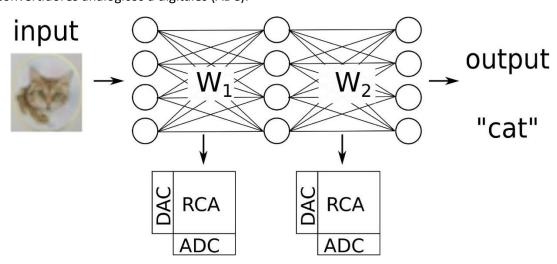

Los diferentes algoritmos en los que se basa la IA necesitan una potencia de cálculo importante, lo que implica la utilización de arquitecturas en las que se puedan realizar muchas operaciones aritméticas, como multiplicaciones y acumulaciones de forma simultánea. Esta necesidad impone arquitecturas paralelas, que implementadas en tecnologías de semiconductores con nodos tecnológicos superiores a los 100 nm tendrían superficies prohibitivas en coste y en consumo de energía, por lo que su implementación ha sido posible a medida que los nodos tecnológicos, siguiendo la ley de Moore, han ido descendiendo de tamaño por debajo de 40 nm y la frecuencia de operación ha ido subiendo hasta el orden de 1 GHz., lo que también ha provocado un **consumo considerable de energía**, que es uno de los desafíos de las arquitecturas actuales de los chips de IA.

<u>Figura 2</u>. El círculo virtuoso entre la Inteligencia artificial y las tecnologías de semiconductores. Fuente: elaboración propia

Por otro lado, la aplicación de la IA para obtener chips de IA que puedan implementar algoritmos de IA más eficientemente conduce a un círculo virtuoso entre la IA y la tecnología de semiconductores. La IA mejora las **herramientas EDA³ para el diseño de chips** con mejor rendimiento, potencia, área, costo y "time to market" (PPACt). El ciclo virtuoso de IA que impulsa la propia IA ha arraigado en la industria de los semiconductores, impulsando nuevas arquitecturas y, en algunos casos, reduciendo drásticamente los ciclos de desarrollo a prácticamente la mitad, (por ejemplo de dos años a uno) aumentando considerablemente la productividad del diseño, uno de los factores de coste más elevados para obtener un chip IA.

La IA también se aplica para mejorar el rendimiento de los procesos de fabricación de los chips. A su vez, la **evolución constante de los nodos tecnológicos** permite reducir el tamaño de los chips y aumentar la velocidad de procesado. Con el concepto "More Moore" se consigue aumentar la velocidad de procesado, lo que mejora considerablemente las aplicaciones de la IA.

La industria de semiconductores es al mismo tiempo **impulsora** y **consumidora** de sistemas de IA. Sin lugar a duda, la IA será una característica destacada de la industria de semiconductores durante las próximas décadas.

### Uso dual de los semiconductores

El **uso dual de los semiconductores** se refiere a su capacidad de ser utilizados tanto en aplicaciones **civiles** como **militares**. Esta característica los convierte en una <u>tecnología</u> <u>estratégica</u> y, a menudo, objeto de regulaciones gubernamentales y restricciones comerciales.

Ejemplos de uso dual:

- <u>Sensores y comunicaciones</u>: Chips utilizados en **antenas 5G** o **radares de automóviles** también pueden integrarse en **sistemas de radar militar** o en **equipos de guerra electrónica**.

- Procesadores y Computación de Alto Rendimiento: Un procesador de alto rendimiento como los de AMD o Intel puede ser usado en centros de datos para el entrenamiento de IA y también en simulaciones militares o criptografía avanzada.

- <u>Electrónica de Consumo vs. Militar:</u> Un chip de inteligencia artificial usado en un smartphone puede ser el mismo que se emplea en sistemas de reconocimiento de imágenes en drones militares.

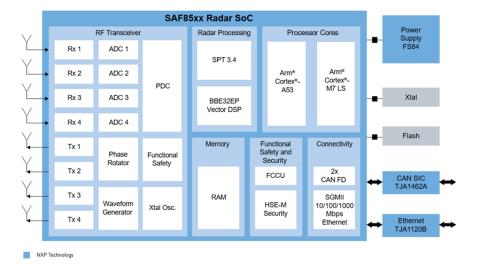

En la Fig. 3 se representa un diagrama de bloques de un SoC, concretamente el SAF85xx de NXP Semiconductor que es claramente de uso dual. En efecto, este SoC es un radar para automoción altamente integrado que opera en la banda de 76 a 81 GHz.

Su utilización en automoción se extiende cada vez más, no solo por la utilización de Sistemas Avanzados de Asistencia al Conductor (ADAS) en los vehículos actuales, sino con el advenimiento

\_

<sup>&</sup>lt;sup>3</sup> Herramientas EDA (Electronic Design Automation) son, principalmente, el conjunto de herramientas software que los ingenieros de diseño microelectrónico utilizan para el diseño, simulación y verificación de los chips. También se consideran herramientas EDA el software para la simulación de procesos tecnológicos y caracterización de dispositivos electrónicos. Igualmente, en la emulación se utilizan equipos hardware programables que interaccionan con las herramientas EDA clásicas como los simuladores y sintetizadores. Actualmente, las herramientas EDA más avanzadas están impulsadas por la IA con objeto de aumentar la productividad del diseño de los chips y su eficiencia.

de los vehículos autónomos donde este tipo de circuitos, y la aplicación de la IA en la computación en el borde, serán ampliamente utilizados.

<u>Figura 3</u>. Diagrama de bloques del SoC (System on Chip) SAF85xx Radar para automoción de NSP Semiconductor. Fuente: <u>SAF85xx</u>, <u>Radar SoC | NXP Semiconductors</u>

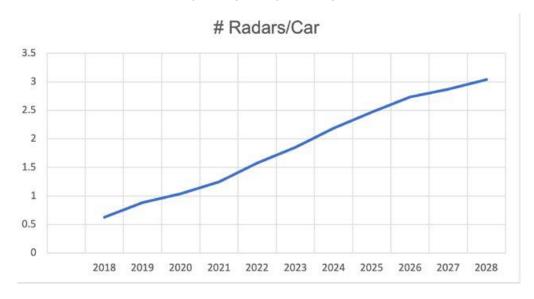

En la Figura 4, puede verse el aumento progresivo de sensores de radar en los vehículos. Buenos ejemplos son el frenado de emergencia autónomo y el control de puntos ciegos, que utilizan sensores de radar. Este razonamiento sobre la utilización de sensores de radar para ADAS y vehículos autónomos (sin conductor), puede aplicarse también para vehículos militares. La tecnología es la misma. Únicamente los chips además de cumplir la norma de Calidad en Automoción AEC-Q100, tendrían que adaptarse para cumplir la norma MIL-STD.

<u>Figura 4</u>. Número medio de sensores de radar por vehículo a lo largo del tiempo. Fuente <u>ADAS</u>

<u>Architectures and radar processing</u>

### Impulsores actuales de la industria de semiconductores

En cuanto al volumen de producción que permite mantener la capacidad de las fábricas de semiconductores el **motor principal es el sector civil**. En efecto, los impulsores clave en el sector civil, son actualmente:

- Inteligencia Artificial y Cloud Computing: Empresas como NVIDIA, Google y Microsoft están liderando la demanda de semiconductores avanzados para IA.

- Automoción y Electrónica de Consumo: La industria de los vehículos eléctricos (Tesla, BYD) y los smartphones (Apple, Samsung) requieren chips más potentes.

- **Computación Cuántica y 5G/6G**: Avances en telecomunicaciones impulsan el desarrollo de semiconductores especializados.

En Defensa muchos chips tienen un volumen de producción reducido, comparado con el sector civil, además de los requerimientos específicos de una mayor fiabilidad y un funcionamiento en un rango de temperaturas más extenso que el rango de temperaturas comercial, lo que conduce a un precio unitario mayor por chip, en igualdad de funcionalidad con el sector civil pues los costes fijos deben distribuirse en un menor número de unidades. Sin embargo, el sector de la Defensa es, claramente, un impulsor estratégico:

- **Autonomía en chips nacionales**: Países como EE.UU. y China están desarrollando fábricas locales para reducir la dependencia extranjera.

- **Supercomputadoras y Ciberseguridad**: Aplicaciones militares de alto secreto dependen de chips avanzados para simulaciones y criptografía.

- Armas Autónomas y Guerra Electrónica: Sistemas como los drones de combate o los misiles guiados requieren semiconductores especializados

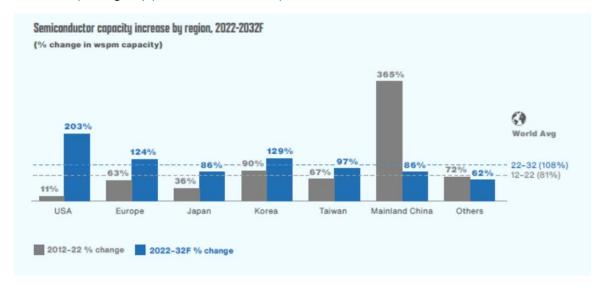

El sector civil lidera la demanda en volumen, pero el sector defensa es un impulsor estratégico clave. Gobiernos como el de EE.UU. están invirtiendo miles de millones en fábricas locales (TSMC, Intel, Samsung en Arizona) para garantizar la producción de chips sin depender de Asia, lo que demuestra el papel clave del sector militar en la planificación a largo plazo.

En definitiva, aunque los consumidores y la IA lideran el crecimiento de la industria, la geopolítica y la defensa están definiendo las estrategias de producción y seguridad de suministro

### Evolución de la Tecnologías de Semiconductores

Desde la invención del transistor en los Bell Labs en 1947 hasta la actualidad, han transcurrido 78 años, en los que la microelectrónica, la rama de la electrónica que se ocupa de los circuitos y componentes electrónicos miniaturizados a escala micrométrica (µm) y nanométrica (nm), ha sido la base física sobre la que se ha edificado la digitalización que ha propiciado las telecomunicaciones modernas, tanto cableadas como inalámbricas, la informática, Internet, la robótica y multitud de aplicaciones en la mayoría de actividades industriales, de salud, de ocio, financieras y económicas, que han conducido a un importante aumento de la productividad.

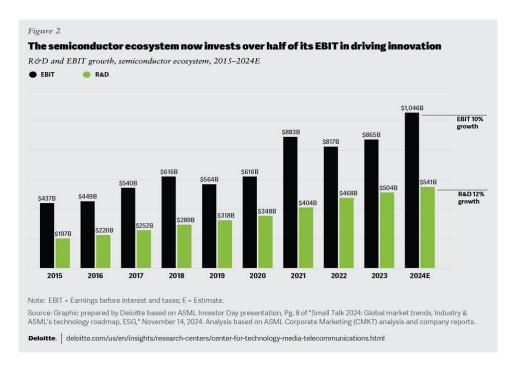

Estos avances se han producido por la constante inversión en I+D e innovación del diseño y procesos tecnológicos de los semiconductores, que han permitido aumentar el número de transistores por unidad de superficie de forma casi continua desde la invención del circuito integrado monolítico en 1959 por Kelby y Noyce.

### Ley de Moore

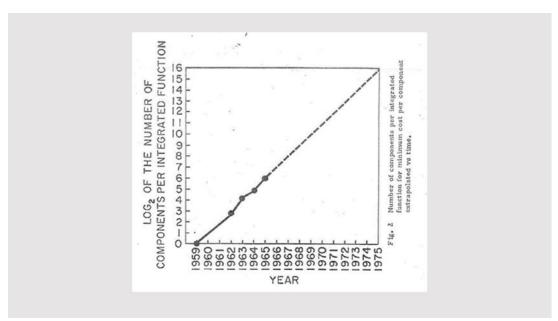

En 1965, el cofundador de Intel, Gordon Moore, predijo que el número de transistores en un chip se duplicaría aproximadamente cada dos años, con un aumento mínimo en el costo. Esta predicción se conoce como "Ley de Moore" (véase la figura 5).

<u>Figura 5</u>. Gráfico original de Gordon Moore en el que en ordenadas se expresa el logaritmo en base 2 del "número de componentes por función integrada" y en abscisas el año. Fuente: (Moore, April 1965)

Como comenta (Kelleher, 2022): "Durante más de 40 años, los ingenieros de Intel han innovado continuamente para integrar cada vez más transistores en chips cada vez más pequeños y mantener el ritmo de la Ley de Moore. A mediados y finales de la década de 2010, como ya lo ha hecho en varias ocasiones anteriores, la industria predijo que «la Ley de Moore ha muerto». Parafraseando un dicho famoso, creo que los informes sobre la muerte de la Ley de Moore son muy exagerados. La innovación no ha muerto, y mantendremos la Ley de Moore como siempre lo hemos hecho, mediante la innovación: innovación en procesos, en el empaquetado y en la arquitectura. Será un desafío, como siempre, e Intel está a la altura".

En efecto, la Ley de Moore se ha ido cumpliendo gracias al esfuerzo en innovación que ha efectuado, no solo Intel, sino todos los fabricantes de semiconductores, aunque en Intel ha sido su caballo de batalla durante las últimas cuatro décadas.

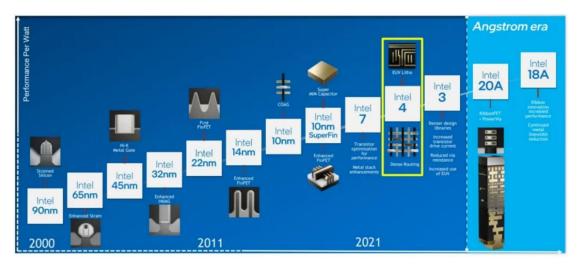

<u>Figura 6</u>. Muestra las innovaciones en proceso realizadas por Intel a lo largo del tiempo. En el eje de ordenadas se refleja las "Prestaciones por watio". Fuente: (Kelleher, 2022)

Las innovaciones de proceso a lo largo del tiempo pueden observarse en la figura 6. A lo largo de los años han ido introduciéndose verdaderas innovaciones que han permitido el cumplimiento de la Ley de Moore. Con inventos como la tecnología de puerta metálica de alta k<sup>4</sup>, los transistores 3D tri-gate y el silicio tensado<sup>5</sup>, Intel ha desarrollado constantemente tecnologías innovadoras para mantenerse al día con la Ley de Moore. A finales de la década de 2000, a medida que las dimensiones físicas seguían reduciéndose, la industria se dio cuenta de que se necesitaban áreas adicionales de innovación, como la ciencia de los materiales, la nueva arquitectura de procesos y la co-optimización de la tecnología de diseño (DTCO), para seguir el ritmo.

<sup>4</sup> A medida que se han ido escalando los dispositivos hacia dimensiones más reducidas, el dieléctrico de puerta que separa la puerta del canal MOS ha ido disminuyendo su grosor para mantener el rendimiento del dispositivo. Sin embargo, el dieléctrico usado en los procesos ha sido siempre el SiO<sub>2</sub> y este material tiene un límite si el espesor de la capa de SiO<sub>2</sub> es inferior a ~1 nm, la corriente de fuga debida al efecto túnel cuántico empieza a predominar, lo que causa graves problemas en el consumo de energía y el rendimiento del dispositivo. Este obstáculo técnico se ha superado reemplazando SiO<sub>2</sub> con aislantes que poseen constantes dieléctricas altas (alto-κ). Con dieléctricos de alto-κ, el espesor dieléctrico se puede aumentar con la misma capacitancia, suprimiendo así la corriente de fuga. Actualmente, los **dieléctricos**

**de alto-κ** preferidos son  $HfO_2$ , el  $ZrO_2$  y el  $Al_2O_3$

<sup>&</sup>lt;sup>5</sup> La **mejora de la movilidad** obtenida mediante la aplicación de la deformación adecuada (El silicio tensado es una capa de silicio en la que los átomos de silicio se estiran más allá de su distancia interatómica normal.) proporciona una mayor velocidad de los portadores de carga en los canales MOS y una mayor corriente de excitación, respectivamente, con la misma tensión de alimentación y el mismo espesor de óxido de puerta. Esto implica que se deben utilizar óxidos de puerta más gruesos o una tensión de alimentación más baja para una corriente de excitación fija, lo que mitiga la relación de compensación entre la corriente de excitación, el consumo de energía y los efectos de canal corto.

También el encapsulado ha seguido evolucionando de forma paralela a la evolución del proceso tecnológico.

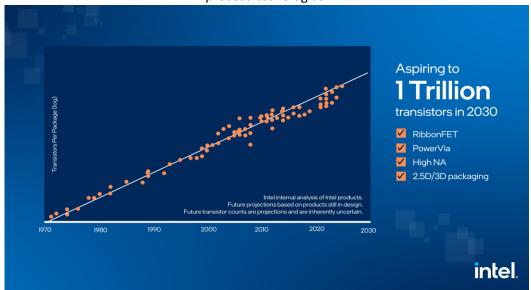

<u>Figura 7</u>. Ley de Moore, número de transistores por dispositivo: Pasado, presente y futuro. Fuente: : (Kelleher, 2022)

En la figura 7, puede observarse el número de transistores por dispositivo a lo largo de estos años. Este número, que indica que se dobla cada par de años, de acuerdo con lo que predice la Ley de Moore, solo se ha podido lograr con una apuesta total por la innovación. Durante los primeros 40 años, las ganancias provinieron principalmente de las innovaciones en el proceso tecnológico. En el futuro, las ganancias provendrán de las innovaciones tanto en el proceso como en el encapsulado. Intel y otros fabricantes consideran que los procesos tecnológicos seguirán ofreciendo mejoras históricas en densidad, mientras que las tecnologías de apilamiento 2D y 3D brindan a los arquitectos y diseñadores más herramientas para aumentar la cantidad de transistores por dispositivo.

En resumen, según (Kelleher, 2022): "cuando consideramos todas las innovaciones en procesos y empaquetado avanzado, hay numerosas opciones disponibles para seguir duplicando la cantidad de transistores por dispositivo al ritmo que demandan nuestros clientes. La Ley de Moore solo se detiene cuando se detiene la innovación, y la innovación continúa sin cesar en Intel en procesos, empaquetado y arquitectura. Seguimos firmes en nuestra aspiración de entregar aproximadamente 1 billón de transistores en un solo dispositivo para 2030". Intel-Moores-Law-Investor-Meeting-Paper-final.pdf

### Concepto de Nodo Tecnológico y su evolución

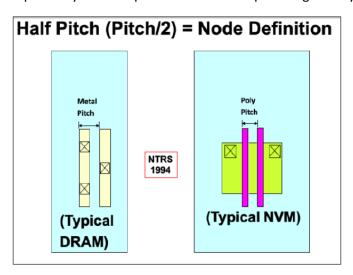

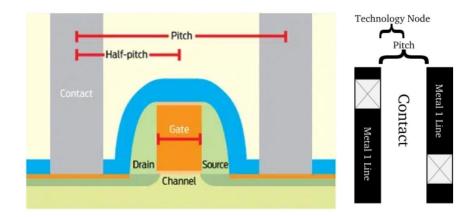

El término **"nodo" en la tecnología de semiconductores** se originó a partir de la medida de la mitad del paso de la celda de memoria de un chip DRAM<sup>6</sup>.

<sup>&</sup>lt;sup>6</sup> DRAM: Memoria de Acceso Aleatorio Dinámica. Es una memoria de lectura y de escritura de acceso aleatorio. El tiempo de acceso es rápido y tiene la mayor densidad, ya que un bit se almacena en un único transistor. Para mantener la información, la memoria necesita "refrescarse" (un reloj debe actuar constantemente) lo cual implica que el consumo de energía sea considerable. Es una memoria volátil, es decir, que, al apagar la alimentación, la memoria no retiene la información.

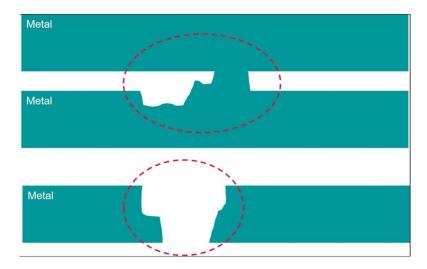

Dado que las mayores capacidades se lograron a través de una mayor densidad, fue la DRAM la que se convirtió en el impulsor de la escalabilidad tecnológica. El nombre del nodo generalmente se alinea con la mitad del paso, conocido como "medio paso" (half-pitch), del área activa en la matriz de celdas de memoria. El medio paso de la celda de memoria en un chip DRAM es una dimensión crucial que influye en la capacidad total del chip. Ver Figuras 8 y 9.

<u>Figura 8</u>. Definición de nodo tecnológico: Mitad del paso (Half pitch) del área activa en una celda de memoria DRAM. Fuente: 2022IRDS ES.pdf

<u>Figura 9</u>. Definición de nodo tecnológico: Mitad del paso (Half Pitch) visto en sección. Fuente: <u>All about Technology Node | LinkedIn</u>

La definición de nodo tecnológico es muy importante porque determina propiedades esenciales del chip, como frecuencia de operación, densidad de este por mm², rendimiento de la oblea y otras.

A medida que los fabricantes de semiconductores siguieron aplicando la Ley de Moore (la observación de que la cantidad de transistores en un microchip se duplica aproximadamente cada dos años), se encontraron con obstáculos importantes a finales del siglo XX.

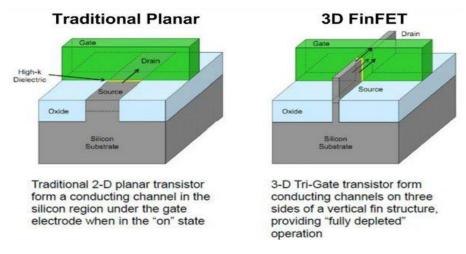

Los MOSFET planares tradicionales (véase la figura 10 izquierda) que se construían en capas superpuestas sobre el sustrato de silicio, se estaban acercando a sus límites físicos. Estos límites se debían principalmente a problemas relacionados con la corriente de fuga y la disipación de potencia, que se volvieron cada vez más problemáticos a medida que los transistores seguían reduciéndose de tamaño. Para superar estos desafíos, los ingenieros y científicos comenzaron a

explorar diseños alternativos de transistores. Uno de los avances se produjo en forma de *FinFET* (*transistores de efecto de campo Fin*). Véase figura 10 (derecha).

<u>Figura 10</u>. Transistor MOSFET tradicional Planar (izda.) y Transistor FinFET (3D). Fuente: Semiconductor Engineering

<u>Figura 11</u>. Evolución de la estructura de los MOSFET: Planar, FinFET y GAA FET. Fuente: Semiconductor Engineering

Mejoras sobre la tecnología planar:

- Menor corriente de fugas

- Mejora de las prestaciones: Velocidad de conmutación más alta.

- Mejora de le eficiencia energética.

- Continuación del escalado -> ¡Se sigue salvando la Ley de Moore!

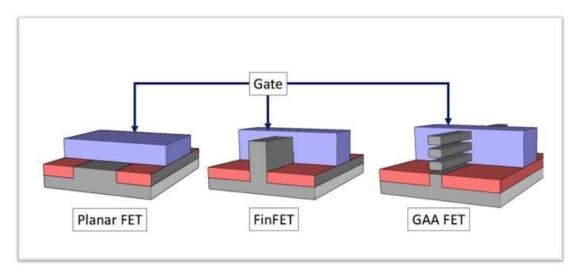

Así pues, la reducción de las dimensiones del nodo tecnológico no ha sido simplemente una reducción de dimensiones clásica, sino que ha habido que innovar en materiales, procesos y dispositivos. Véase la Fig. 11 en la que se ve que a partir de 22nm, se abandona la tecnología planar tradicional y se introduce el FinFET, para evolucionar a partir de 7nm a los dispositivos FET GAA (Gate-All-Around). FinFET y GAA son dispositivos 3D, en contraposición con la tecnología Planar.

La reducción de dimensiones de los dispositivos ha posibilitado integrar muchos más dispositivos (circuitos más complejos, verdaderos sistemas) en la misma área por lo que a media que disminuía el tamaño del nodo el coste del diseño del chip aumentaba considerablemente pues el diseño suele ser un sistema más complejo. Al mismo tiempo, para una misma oblea de 300 mm. a medida que se escalaba hacia abajo (para la misma complejidad de circuito) se obtenían precios unitarios más bajos (salían más chips por oblea). Sin embargo, los costes de fabricación de los prototipos (NRE) son más elevados pues, la amortización de equipos, así como el coste de las máscaras (procesos más complejos y dimensiones más pequeñas) son mayores.

En la figura 12 puede apreciarse el aumento del coste del diseño del chip (Ingeniería de diseño + NREs (fabricación, encapsulado y prueba de prototipos) en función del nodo tecnológico utilizado.

Figura 12. Coste del diseño de un chip en función del nodo tecnológico. Fuente: (Khan & Mann, April 2020)

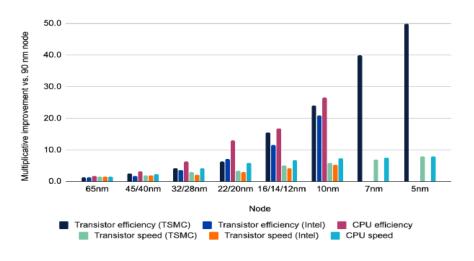

Las mejoras en prestaciones de los nodos más avanzados con respecto a la tecnología de 90 nm pueden observarse en la figura 13. En el caso de la eficiencia del transistor, los del nodo de 5nm son 50 veces las del nodo de 90 nm.

<u>Figura 13</u>. Mejoras en la eficiencia y la velocidad medidas en comparación con el nodo de 90 nm. Fuente: (Khan & Mann, April 2020)

### Hoja de ruta IRDS

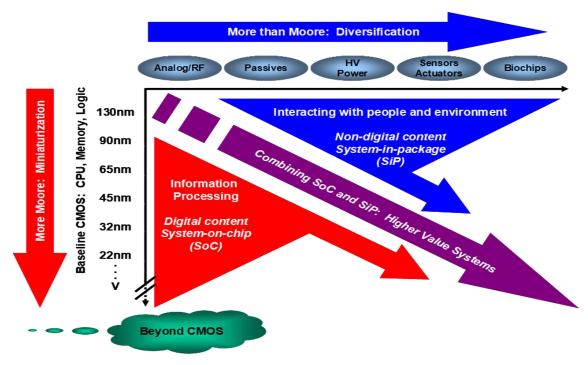

La **Hoja de Ruta Internacional para Dispositivos y Sistemas (IRDS)** define las tendencias clave en tecnología de semiconductores (véase la figura 14), incluyendo los tres conceptos siguientes:

### 1. "More Moore" (MM)

- Se refiere al escalado continuo de la tecnología CMOS según la Ley de Moore, que predice que el número de transistores en un circuito integrado se duplica aproximadamente cada dos años.

- Enfoque: Mejorar el rendimiento, reducir el consumo de energía y aumentar la densidad de transistores.

- Ejemplos de tecnologías:

- Transistores FinFET y Gate-All-Around (GAA)

- Litografía ultravioleta extrema (EUV)

- Arquitecturas avanzadas de transistores 3D

### 2." More than Moore"

- Se extiende más allá del simple escalado de transistores al integrar funcionalidades no digitales (p. ej., analógicas, RF, MEMS, fotónica) en dispositivos semiconductores.

- Enfoque: Diversificar las funcionalidades para permitir mejoras a nivel de sistema en lugar de simplemente aumentar la densidad de transistores. Ejemplos de tecnologías:

- Sistema en chip (SoC) y sistema en paquete (SiP)

- MEMS (sistemas microelectromecánicos)

- Circuitos de radiofrecuencia y ondas milimétricas para 5G/6G

- Fotónica integrada para comunicaciones ópticas

<u>Figura 14.</u> Hoja de ruta de los sistemas integrados (IRDS): Ley de Moore (More Moore) y More than Moore (MtM) (Diversificación). Combinando en un solo encapsulado SoC y MtM en SiP para obtener sistemas de más valor. Fuente: (IRDS, 2023)

### 3." Beyond CMOS"

- Se refiere a las tecnologías post-CMOS que exploran paradigmas informáticos completamente nuevos, más allá de los transistores tradicionales basados en silicio.

- Enfoque: Superar las limitaciones físicas y de potencia del escalado de CMOS mediante el aprovechamiento de materiales y arquitecturas informáticas alternativas.

Ejemplos de tecnologías:

- Computación cuántica (cúbits)

- Computación neuromórfica (arquitecturas inspiradas en el cerebro)

- Espintrónica (utilizando el espín del electrón para el procesamiento de datos)

- Materiales 2D (p. ej., grafeno, dicalcogenuros de metales de transición<sup>7</sup>)

Estos tres enfoques se complementan: «More Moore» impulsa el escalado convencional, «More than Moore» integra nuevas funcionalidades y «Beyond CMOS» investiga futuros sustitutos de las tecnologías informáticas tradicionales.

### "More Moore"

Figura 15. Big Data y Datos Instantáneos. Fuente: (IRDS MM, 2023)

La Ley de Moore y los conceptos de "More Moore" para el escalado de transistores permiten tecnologías como los sistemas en chip (SoC), con requisitos de rendimiento que implican un consumo excesivo de energía y un ancho de banda de interconexión limitado. La interacción entre big data y datos instantáneos presenta desafíos y limitaciones que el IRDS aborda en la hoja de ruta de "More Moore". El escalado de sistemas, gracias al escalado de Moore, se ve cada vez más dificultado por la escasez de recursos como la energía y el ancho de banda de datos. Esto se ha vuelto aún más complejo debido a los requisitos de una interacción fluida entre el big data y los datos instantáneos (Ver Fig. 15). La generación instantánea de datos requiere dispositivos de consumo ultra bajo con función de "siempre activo" ("always-on"), así como dispositivos de alto rendimiento que puedan generar los datos al instante. El big data requiere abundantes recursos de computación, ancho de banda de comunicación y memoria para generar

<sup>&</sup>lt;sup>7</sup> Los dicalcogenuros de metales de transición (TMD) son materiales bidimensionales con notables propiedades semiconductoras y elevados coeficientes de absorción óptica.

el servicio y la información que necesitan los clientes. La necesidad de datos para computación se aceleró con el **aumento de las cargas de trabajo de IA**.

El Equipo de *More Moore International Focus (IFT)* de la Hoja de Ruta Internacional de Dispositivos y Sistemas (IRDS) proporciona los requisitos físicos, eléctricos y de confiabilidad para las tecnologías de lógica y memoria con el fin de mantener el escalado de potencia, rendimiento, área y costo (PPAC) para aplicaciones en el borde y en la nube. Esto se realiza en un horizonte temporal de 15 años para la fabricación convencional/de alto volumen (HVM).

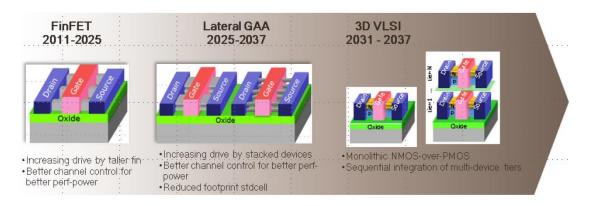

<u>Figura 16</u>. Evolución de las arquitecturas de dispositivos en la hoja de ruta de "More Moore" del IRDS. Fuente: (IRDS MM, 2023 )

Es probable que el finFET se mantenga hasta 2025. En 2022, ya se inició la transición a dispositivos GAA laterales debido a las limitaciones del rendimiento limitado de una sola aleta (finFET), como resultado de la despoblación de aletas y el escalado del ancho de aleta (saturando el escalado de la Lgate para mantener el control electrostático). La mitigación de la capacitancia parásita, el ancho de accionamiento efectivo (Weff) y la integración de la puerta metálica de reemplazo (RMG) siguen siendo el desafío para mantener la adopción de GAA en múltiples nodos. La evolución proyectada de las arquitecturas de dispositivos se muestra en la Figura 16. Se proyecta que el FET complementario (CFET) será la evolución posterior de los GAA laterales en formato 3D, donde los dispositivos N se apilarán sobre los dispositivos P.

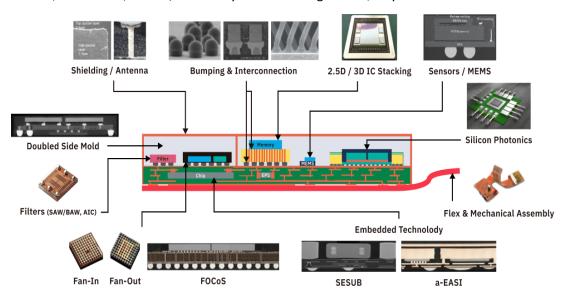

### "More than Moore"

"More than Moore" se refiere a la incorporación en los dispositivos de funcionalidades que no necesariamente se escalan según la Ley de Moore, pero que <u>aportan valor añadido de diferentes maneras</u>. El enfoque "More than Moore" permite que las funcionalidades no digitales (por ejemplo, comunicación por radiofrecuencia, control de potencia, componentes pasivos, sensores, actuadores) migren del nivel de la placa del sistema al encapsulado (SiP) o al chip (SoC).

Además, la integración cada vez más íntima de software integrado complejo en los SoC y SiP significa que el software también podría tener que convertirse en un tejido en consideración que afecte directamente al escalado del rendimiento. (Co-diseño Hw/Sw)

El objetivo de "More than Moore" es ampliar el uso de la tecnología basada en silicio desarrollada en la industria de la microelectrónica para <u>proporcionar nuevas funcionalidades</u> <u>no digitales</u>. A menudo aprovecha las capacidades de escalado derivadas de los desarrollos de "More Moore" para incorporar funcionalidad digital y no digital en sistemas compactos y, eventualmente, en sistemas de sistemas.

"More than Moore" enfatiza las innovaciones en otros aspectos del diseño y la fabricación de chips para satisfacer las crecientes demandas de diversas aplicaciones. (IRDS MtM, 2023)

### "Beyond CMOS"

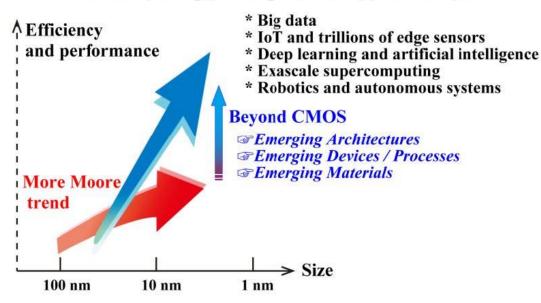

A medida que el escalado dimensional de los CMOS se acerca a **límites fundamentales**, se están explorando **nuevos dispositivos de procesamiento de información y microarquitecturas para funciones existentes y nuevas**.

Esto está impulsando el interés en nuevos dispositivos para el procesamiento de información y la memoria, nuevas tecnologías para la **integración heterogénea** de múltiples funciones y nuevos paradigmas para la arquitectura de sistemas.

Los nuevos paradigmas informáticos y las nuevas aplicaciones (por ejemplo, big data, **Internet** de las cosas (IoT), inteligencia artificial, sistemas autónomos, computación a exaescala) introducen mayores requisitos de rendimiento y eficiencia, que son cada vez más difíciles de cumplir para las saturadas tecnologías de **More Moore**.

Las tecnologías **Beyond-CMOS** pueden proporcionar los dispositivos, procesos y arquitecturas necesarios para la nueva era de la informática. En Beyond-CMOS se contemplan tecnologías como las "Memorias emergentes", los nanocables, la computación cuántica, etc. (ver figura 17). Trata de superar las limitaciones de la Ley de Moore, en eficiencia y prestaciones, mediante la combinación de materiales, dispositivos y arquitecturas emergentes.

### Novel computing paradigms and application pulls

<u>Figura 17</u>. Relación entre More Moore, Beyond CMOS y nuevos paradigmas computacionales y sus aplicaciones. Fuente: (IRDS BC, 2023)

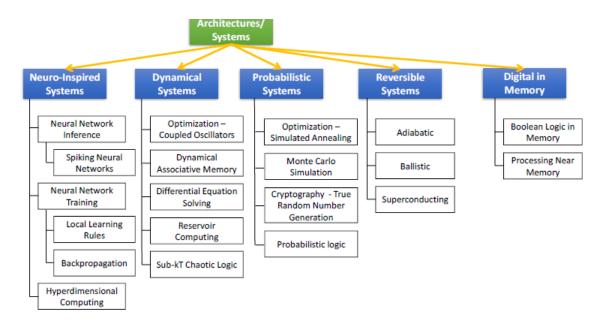

<u>Figura 18</u>. Arquitecturas/Sistemas para nuevos paradigmas computacionales enumerados por IRDS en la tendencia "Beyond CMOS". Requieren co-diseño con dispositivos emergentes. Fuente: (IRDS BC, 2023)

Las nuevas arquitecturas y sistemas que impulsan las nuevas aplicaciones como la robótica y los sistemas autónomos, la IA y el Aprendizaje profundo, el IoT y la IA en el borde con millones de sensores, la supercomputación, etc. exigen nuevos dispositivos que superen las limitaciones del final de la Ley de Moore, los dispositivos emergentes (dispositivos sinápticos, dispositivos estocásticos y dispositivos osciladores) (IRDS BC, 2023).

### SoC y SiP

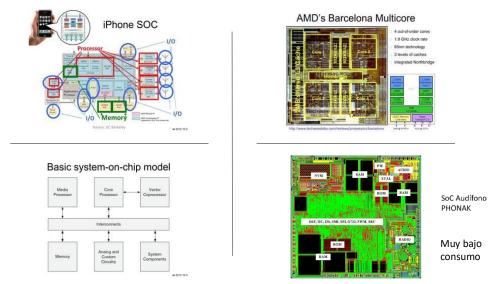

Los sistemas electrónicos actuales pueden integrarse en un único chip. En este caso se habla de un **SoC** (System on Chip) (Ver figura 19). Sus principales características son:

- Integra múltiples componentes (CPU, GPU, memoria, E/S, etc.) en una única pieza de silicio (Circuito integrado monolítico).

- Diseñado para aplicaciones compactas, de alto rendimiento y bajo consumo.

- Optimizado para tareas específicas (p. ej., smartphones, dispositivos IoT, sistemas embebidos). Su fabricación se basa generalmente en procesos avanzados de fabricación CMOS.

- Ofrece comunicación de alta velocidad entre componentes gracias a interconexiones cortas.

- Escalabilidad y flexibilidad limitadas en comparación con las soluciones multichip.

### Ejemplos de SoC

<u>Figura 19</u>. Cuatro ejemplos de SoC: a) Diagrama de bloques de SoC en iPhone; b) Fotomicrografía del Chip "Barcelona Multicore" de AMD (4 cores.)Fuente: <u>AMD Barcelona Architecture Launch: Native Quad-Core | HotHardware</u>; c) Un diagrama de un modelo de SoC básico (Procesador, Memoria, partes analógicas y ADCs/DACs,...) y d)Fotmicrografía SoC audífono (mixed analog-digital) Phonak de muy bajo consumo.

Características principales de un SiP (Ver figura 20):

- Combina múltiples dados (chips) independientes en un único encapsulado.

- Puede integrar diferentes tecnologías (p. ej., CMOS, RF, MEMS, fotónica, electrónica de potencia).

- Permite un diseño modular y flexibilidad para integrar diversas funcionalidades.

- Se utiliza en aplicaciones como 5G, automoción, aceleradores de IA y wearables.

Permite utilizar técnicas de encapsulado avanzadas (p. ej., integración 2.5D/3D, vías a través de silicio).

- Es más fácil combinar componentes que en un SoC.

Figura 20. Representación de un SiP que incluye chips, y MEMs.

| Característica             | SoC (System on Chip)                                                   | SiP (System in Package)                                                        |

|----------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Integración                | Todos los componentes en una único "dado"                              | Múltiples "dados" independientes en un encapsulado                             |

| Tamaño                     | Más compacto                                                           | Ligeramente más grande debido a múltiples "dados"                              |

| Rendimiento                | Comunicación de alta velocidad entre componentes                       | Ligeramente menor debido a la comunicación entre chips                         |

| Eficiencia<br>energética   | Menor consumo de energía debido a interconexiones cortas               | Consumo de energía ligeramente mayor debido a enlaces entre chips              |

| Flexibilidad               | Menos flexible; todo el diseño debe optimizarse en conjunto            | Más flexible; permite combinar diferentes tecnologías de chip                  |

| Complejidad de fabricación | Requiere fabricación avanzada de semiconductores (p. ej., FinFET, EUV) | Utiliza técnicas de encapsulado<br>avanzadas (p. ej., apilamiento 2.5D,<br>3D) |

| Aplicaciones               | Smartphones, sistemas<br>embebidos, IoT, chips de IA                   | 5G, automoción, aceleradores de<br>IA, módulos de RF                           |

| Escalabilidad              | Limitada debido a la naturaleza monolítica                             | Alta escalabilidad mediante la adición de más matrices                         |

<u>Tabla 1</u>. Comparación entre SoC (System on Chip) y SiP (System in Package)

El SoC es ideal para aplicaciones de alto rendimiento y bajo consumo que requieren una integración estrecha, mientras que el SiP proporciona mayor flexibilidad y modularidad para diversos diseños de sistemas.

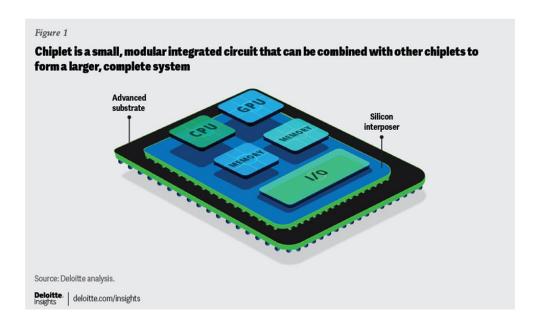

En algunas aplicaciones, muchas veces, interesa más diseñar un sistema utilizando el concepto de Chiplet que diseñar el sistema en un único circuito integrado monolítico (SoC). Los **chiplets** son procesadores segmentados. En lugar de consolidar cada componente en un solo chip (lo que se conoce como enfoque monolítico), se fabrican secciones específicas como chips separados. Estos chips individuales se ensamblan en un solo encapsulado mediante un complejo sistema de conexión. (Evanson, 2025)

Un **chiplet** es un pequeño circuito integrado (CI) monolítico especializado, diseñado para combinarse con otros chiplets dentro de un único encapsulado y formar un sistema completo (Ver Fig. 21). En lugar de diseñar un gran chip monolítico, se pueden fabricar chiplets más pequeños por separado e integrarlos en un encapsulado, lo que mejora el rendimiento y la escalabilidad.

### Aspectos clave de los chiplets:

- Enfoque modular para el diseño de chips.

- Optimizado para funciones específicas (p. ej., CPU, GPU, memoria, aceleración de IA).

- Permite la reutilización de diseños probados, lo que reduce los costes de desarrollo.

- Se suelen conectar mediante interconexiones de alta velocidad como UCIe, EMIB o TSV.

- Se encuentra en la computación de alto rendimiento, aceleradores de IA y procesadores avanzados (p. ej., AMD, Intel, NVIDIA).

<u>Figura 21</u>. Sistema integrado (SiP) que monta varios chiplets (CPU, GPU, Memorias, I/O). Fuente: Deloitte análisis.

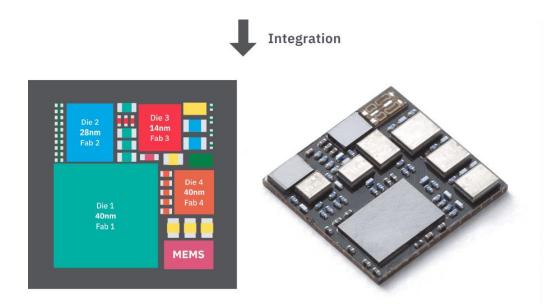

La **Integración Heterogénea** (HI) se refiere al proceso de combinar diversos materiales semiconductores, tecnologías o componentes funcionales en un único encapsulado o sistema. Esta integración permite una funcionalidad avanzada que no se puede lograr con un solo circuito integrado monolítico.

Aspectos Clave de la Integración Heterogénea:

- Combina diferentes tecnologías (p. ej., CMOS, MEMS, fotónica, RF, electrónica de potencia).

- Puede incluir diferentes materiales (p. ej., silicio, GaN, InP, grafeno).

- Se utiliza en encapsulados 2.5D/3D, SiP y sistemas semiconductores avanzados.

- Se encuentra en aplicaciones como 5G, IA, automoción, defensa, aeroespacial y dispositivos médicos.

<u>Figura 22a</u>. Chips y MEMs que forman los componentes del sistema integrar Fuente: <u>Heterogeneous</u> Integration (HI) | ASE

<u>Figura 22b</u>. El sistema con los componentes ya interconectados (integración heterogénea) para encapsularse en un SiP. Fuente: <u>Heterogeneous Integration (HI) | ASE</u>

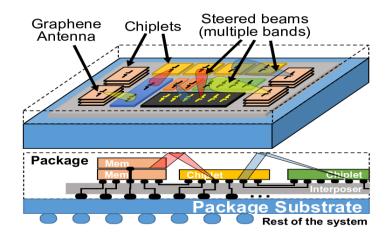

Las figuras 22a y 22b muestran un esquema de los diferentes circuitos integrados monolíticos y MEMs antes de interconectarse (Fig. 22a) y después de la interconexión para encapsularse en un SiP (Fig. 22b). La figura 23 es una integración heterogénea que utiliza un interposer de silicio para las interconexiones con componentes de fotónica integrada, antena, filtros SAW, MEMS/sensores y circuitos integrados 2,5D y 3D.

<u>Figura 23</u>. Vista en sección con el interposer que interconecta los diferentes componentes de una Integración heterogénea con diferentes tecnologías. Fuente: <u>Heterogeneous Integration (HI) | ASE</u>

### Chips para aplicaciones en Defensa

Los chips para aplicaciones en defensa, incluyendo el espacio para aplicaciones de defensa y seguridad, están diseñados para ofrecer una durabilidad, seguridad y fiabilidad extremas en entornos hostiles. Son mucho más caros, debido a que tienen, generalmente un volumen de producción mucho más bajo que sus equivalentes en el sector civil, además de que su diseño,

proceso de fabricación, prueba, encapsulado y certificación requieren más equipamiento y tiempo que los chips comerciales. Suelen utilizar tecnología más antigua y probada en lugar de nodos de última generación.

En la tabla 4, se muestran las diferencias fundamentales entre los chips para la defensa y el espacio y los chips comerciales.

| Característica                     | Chips de grado militar                                           | Chips Comerciales              |  |

|------------------------------------|------------------------------------------------------------------|--------------------------------|--|

| Rango de Temperatura               | -55ºC a + 125ºC                                                  | 0ºC a +70ºC                    |  |

| Resistencia a la radiación         | Sí (rad-hard)                                                    | No                             |  |

| Resistencia a golpes y vibraciones | Alta (MIL-STD.883)                                               | estándard                      |  |

| Características de seguridad       | Anti-manipulación,<br>encriptado, cadena de<br>suministro segura | Seguridad Mínima               |  |

| Nodo del proceso tecnológico       | 90nm, 130nm, 180nm                                               | 5nm, 7nm, 10nm, 28nm           |  |

| Material                           | SOI <sup>8</sup> , SiC, materiales resistentes a la radiación    | Silicio estándard              |  |

| Coste                              | 10 x a 100x más alto                                             | Bajo costo, producción en masa |  |

<u>Tabla 2</u>. Comparación resumida entre las características clave que diferencian a los chips de grado militar (chips para la defensa, la seguridad y el espacio) y los chips comerciales.

### Materiales para la fabricación de chips para la defensa.

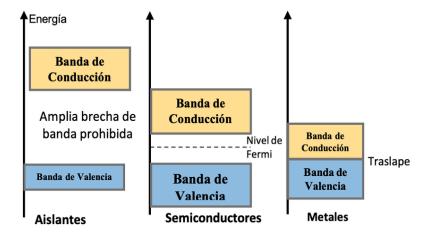

Por materiales, aquí se entiende, básicamente los substratos sobre los que se fabrican los elementos activos que, una vez Inter conexionados, forman los sistemas integrados. Estos substratos son los materiales semiconductores. Se distinguen dos grandes grupos: a) los semiconductores simples, como el silicio y el germanio; y b) los semiconductores compuestos, prioritariamente los del grupo III-V.

Afortunadamente, el silicio es un elemento muy abundante en la naturaleza y el elemento clave en la fabricación de chips semiconductores. En efecto, el silicio, el material principal en el que se basan los chips semiconductores, es el segundo elemento más abundante (28%) en la corteza terrestre, por lo que garantiza un suministro relativamente estable de silicio en el futuro cercano.

### Silicio (Si):

- Banda prohibida: Aproximadamente 1.1 eV.

- Movilidad de electrones: Moderada (alrededor de 1400 cm<sup>2</sup>/V·s).

- Temperatura de operación: Adecuado para aplicaciones a temperatura ambiente.

- Usos comunes: Electrónica, fotovoltaica, y circuitos integrados.

- Ventajas: Abundante, bajo costo y bien desarrollado en la industria.

<sup>&</sup>lt;sup>8</sup> SOI Silicon On Insulator: Es una estructura semiconductora que consta de una capa de silicio monocristalino separada del sustrato principal por una fina capa de aislante.

Figura 24. Estructura de bandas de energía de aislantes, semiconductores y metales

<u>Figura 25</u>. Barra de silicio formada a partir de un cristal de silicio (semilla) por el método de Czochvalski. Las obleas se obtienen cortando con sierras especiales la barra en rodajas.

### Semiconductores compuestos III-V

Los semiconductores III-V se crean mediante la combinación de elementos del grupo III (como el galio, el aluminio y el indio) y del grupo V (incluido el fósforo, el arsénico y el nitrógeno) de la tabla periódica, lo que da como resultado la generación de una estructura de red cristalina con características electrónicas excepcionales. A diferencia del silicio, los semiconductores III-V ofrecen propiedades de banda prohibida directa, lo que proporciona una conversión altamente eficiente de energía de fotones a electrones. Este atributo único hace que los semiconductores III-V sean particularmente adecuados para aplicaciones optoelectrónicas.

### Nitruro de galio (GaN):

- Banda prohibida: Alrededor de 3.4 eV.

- Movilidad de electrones: Alta (aproximadamente 2000 cm²/V·s).

- Temperatura de operación: Excelente para altas temperaturas y alta potencia.

- Usos comunes: Dispositivos de potencia, LED y láseres.

- Ventajas: Alta eficiencia y capacidad para manejar altas tensiones.

El nitruro de galio es un semiconductor compuesto de banda prohibida directa III/V que resulta muy adecuado para transistores de alta potencia capaces de funcionar a altas temperaturas. Desde la década de 1990, se ha utilizado habitualmente en diodos emisores de luz (LED). El nitruro de galio se utiliza en dispositivos de potencia semiconductores, componentes de RF, láseres y fotónica. Se empieza a utilizar GaN en la tecnología de sensores.

En 2006, los transistores GaN, a veces denominados FET de GaN, comenzaron a fabricarse mediante el crecimiento de una fina capa de GaN sobre la capa AIN de una oblea de silicio estándar mediante deposición química en fase de vapor de metal orgánico (MOCVD). La capa AIN actúa como un amortiguador entre el sustrato y el GaN. Este nuevo proceso permitió que los transistores de nitruro de galio se pudieran producir en las mismas fábricas, ya establecidas, que las de silicio, utilizando casi los mismos procesos de fabricación. Al utilizar un proceso conocido, esto permite costos de fabricación bajos y similares y reduce la barrera para la adopción de transistores más pequeños con un rendimiento muy mejorado.

La tecnología de GaN es prometedora en aplicaciones como la electrónica de potencia, los sistemas de RF, la industria automotriz, la industria aeroespacial, las telecomunicaciones y las energías renovables.

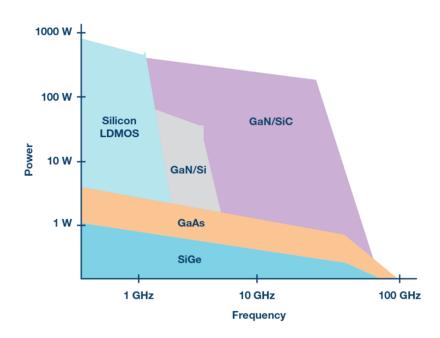

### GaN en defensa

La tecnología de GaN ha desempeñado un papel clave en la mejora de la eficacia y la eficiencia de las <u>operaciones de defensa</u>, desde los <u>sistemas de radar avanzados</u> hasta los <u>sistemas de comunicación</u>. Sus características principales son:

- Alta movilidad de electrones y velocidad de saturación, lo que permite operaciones de alta velocidad. En comparación con el silicio, GaN tiene propiedades de transporte de electrones superiores, lo que permite velocidades de conmutación más rápidas y posibilita el desarrollo de dispositivos de alta frecuencia.

- El ancho de banda prohibida de GaN es otra ventaja clave. Con una banda prohibida aproximadamente tres veces más amplia que el silicio, los semiconductores de GaN exhiben capacidades de alto voltaje de ruptura. Esto permite un manejo eficiente de la energía y los hace adecuados para aplicaciones de alta potencia. Los dispositivos de GaN pueden operar a voltajes más altos sin comprometer el rendimiento, lo que proporciona una mayor confiabilidad y robustez.

- Los semiconductores de GaN también exhiben una excelente conductividad térmica. El material disipa eficazmente el calor, lo que permite una gestión térmica eficaz en aplicaciones de alta potencia. Esta propiedad ayuda a prevenir el sobrecalentamiento y mejora la fiabilidad del dispositivo. Además, la compatibilidad del GaN con temperaturas de funcionamiento más altas en comparación con los semiconductores basados en silicio contribuye aún más a mejorar el rendimiento y la fiabilidad, ya que reduce la necesidad de sistemas de refrigeración complejos.

- Potencial del GaN para dispositivos más pequeños y ligeros. Debido a su alta densidad de potencia y capacidades de miniaturización, los componentes basados en GaN pueden ofrecer salidas de alta potencia mientras ocupan espacios físicos más pequeños.

- Los semiconductores de GaN también son prometedores en términos de eficiencia energética

### Aplicaciones de la tecnología GaN en la industria de defensa.

- La tecnología GaN es valorada por la industria de defensa debido a sus características de rendimiento superiores, que incluyen alta densidad de potencia, eficiencia y confiabilidad. Para empezar, es fundamental para mejorar los sistemas de radar y guerra electrónica (EW), señala "Military Embedded Systems"

- Los componentes basados en GaN se utilizan en radares de matriz de barrido electrónico activo (AESA) y otras aplicaciones de alta potencia debido a su capacidad para ofrecer alta potencia de salida, eficiencia y amplio ancho de banda. Estas características hacen que GaN sea ideal para los sistemas de radar y EW de próxima generación, que requieren un tamaño, peso y potencia (SWaP) reducidos.

- GaN también se utiliza en sistemas de comunicación militar para mejorar el rendimiento y la confiabilidad. Se emplea en módulos multichip para aplicaciones de alta frecuencia, lo que permite una navegación eficiente y el control del tráfico aéreo en tiempo real. La capacidad de GaN para operar a frecuencias más altas lo hace adecuado para bloqueadores militares y radios terrestres

- La tecnología GaN, según Efficient Power Conversion Corporation, es ventajosa para la

gestión de energía en aplicaciones de defensa. Ofrece una mayor densidad de potencia

y una mejor gestión térmica, lo que es crucial para los sistemas que operan en entornos

hostiles. Por ejemplo, los amplificadores de potencia de GaN están reemplazando a los

tubos de ondas progresivas (TWT) tradicionales en aplicaciones espaciales debido a su

mayor confiabilidad y eficiencia.

En la Tabla 3 se indican las energías de banda prohibida para diferentes materiales semiconductores. Los materiales considerados de anchura de banda prohibida grande (salto de energía en eV > 3) son los de fondo verde. Entre ellos están el SiC y el GaN que, por este motivo, son adecuados para Electrónica de potencia.

| MATERIALES SEMICONDUCTORES |                    |                                 |  |  |

|----------------------------|--------------------|---------------------------------|--|--|

| MATERIAL                   | Símbolo<br>Químico | ENERGÍA BANDA<br>PROHIBIDA (eV) |  |  |

| Germanio                   | Ge                 | 0,7                             |  |  |

| Silicio                    | Si                 | 1,1                             |  |  |

| Arseniuro de Galio         | GaAs               | 1,4                             |  |  |

| Carburo de Silicio         | SiC                | 3,3                             |  |  |

| Óxido de Zinc              | ZnO                | 3,4                             |  |  |

| Nitruro de Galio           | GaN                | 3,4                             |  |  |

| Diamante                   | С                  | 5,5                             |  |  |

<u>Tabla 3</u>. Materiales semiconductores y su Energía de banda prohibida en eV (Fogarty, 2019)

<u>Figura 26</u>. Comparación de potencia y frecuencia de diferentes materiales semiconductores en el rango de microondas, que incluye a las ondas milimétricas. Fuente: Analog Devices (Fogarty, 2019)

En las comunicaciones militares y en el IoT militar en el 5G+ y 6G, se utilizarán cada vez más las ondas milimétricas<sup>9</sup>. En efecto, las ondas milimétricas son de gran interés para la Defensa por las ventajas estratégicas que comportan, entre las que destacan:

- Alta resolución → Permite la detección precisa de objetivos.

- Baja interferencia → Menos congestión en comparación con frecuencias más bajas.

- Capacidades de sigilo o secreto → Difícil de detectar con sistemas de radar convencionales.

- Penetración de algunos materiales → Atraviesan la niebla, la lluvia y la ropa.

Aplicaciones de las ondas milimétricas (MMW) en aplicaciones de defensa:

### 1. Sistemas de Radar

Los radares MMW brindan una resolución superior para la detección y el seguimiento de objetivos.

- Las matrices de escaneo electrónico activo (AESA) utilizan ondas milimétricas para la detección furtiva y la guía de misiles.

- Los radares de control de tiro en aviones de combate operan en frecuencias MMW para apuntar con precisión.

<sup>9</sup> Las **ondas milimétricas** (MMW) se refieren a ondas electromagnéticas con frecuencias entre 30 GHz y 300 GHz y longitudes de onda que van desde 1 mm a 10 mm. Estas ondas se ubican entre las frecuencias de microondas e infrarrojas en el espectro electromagnético.

Los radares terrestres utilizan MMW para detectar amenazas que vuelan a baja altura, como los drones

Ejemplo: El radar AN/APG-81 en el avión de combate F-35 utiliza MMW para un seguimiento de alta precisión.

### 2. Armas de energía dirigida (DEW) (Directed Energy Weapons)

Las ondas milimétricas de alta potencia se pueden utilizar como armas para desactivar los dispositivos electrónicos enemigos o causar molestias

- Sistemas de denegación activa (ADS) → Arma de control de multitudes no letal que utiliza MMW de 95 GHz para crear una intensa sensación de ardor.

- Tecnología antidrones → La energía MMW puede inutilizar los UAV (vehículos aéreos no tripulados).

Ejemplo: El sistema ADS ("rayo de calor") del ejército de EE. UU. dispersa multitudes sin fuerza letal.

### 3. Comunicaciones militares seguras

Las frecuencias MMW proporcionan enlaces de comunicación seguros de gran ancho de banda para operaciones militares.

- Las comunicaciones por satélite (SATCOM) utilizan MMW para transmisiones de datos de alta velocidad.

- Las redes de banda ancha tácticas (como las aplicaciones militares 5G) utilizan MMW para compartir datos cifrados de baja latencia.

Ejemplo: Los sistemas de comunicación de banda W (75–110 GHz) se utilizan para la transferencia segura de datos en el campo de batalla.

### 4. Imágenes y vigilancia

Los sistemas de imágenes MMW pueden detectar armas ocultas y amenazas en condiciones de baja visibilidad.

- Puede ver a través de la ropa y los obstáculos (útil para la lucha contra el terrorismo).

- Funciona en la niebla, el polvo y el humo, donde la óptica tradicional falla.

Ejemplo: Las cámaras pasivas de ondas milimétricas detectan objetos al capturar la radiación natural.

### 5. Sistemas de guía de misiles

Los buscadores de ondas milimétricas mejoran la precisión de los misiles.

- Los buscadores de misiles utilizan ondas milimétricas para la guía terminal, lo que permite un seguimiento preciso del objetivo.

- La capacidad de penetración en todo tipo de clima hace que las ondas milimétricas sean útiles en todas las condiciones.

Ejemplo: El misil AGM-114R Hellfire utiliza un radar de ondas milimétricas para la adquisición de objetivos.

No obstante, las grandes ventajas estratégicas del uso de las ondas milimétricas (MMW) en aplicaciones de la defensa, su uso plantea una serie de desafíos, entre los que podemos destacar:

- Absorción atmosférica → Las señales MMW se debilitan en largas distancias, especialmente con lluvia y niebla.

- Alto costo del equipo → La tecnología MMW requiere materiales avanzados y fabricación de precisión.

- **Penetración limitada** → Si bien pueden penetrar la ropa, tienen dificultades con obstáculos densos como paredes y metal.

Entre las tendencias futuras de la utilización de las MMW en Defensa, destaca:

- <u>Integración con IA</u> → Los radares MMW impulsados por IA mejoran la detección autónoma de amenazas.

- Redes de campo de batalla 5G → Comunicación de alta velocidad y baja latencia para centros de comando militar.

- Miniaturización → Los chips MMW compactos mejoran los UAV y los sistemas que usan los soldados.

Las importantes ventajas estratégicas de las MMW en aplicaciones para la defensa dan una relevancia especial a los circuitos diseñados y fabricados con GaN. En efecto, en la Fig. 26, puede apreciarse la ventaja de los circuitos GaN/SiC sobre otras tecnologías como GaAs, SiGe y Silicio en las frecuencias correspondientes a las MMW. GaN es más eficiente energéticamente que el silicio para RF 5G.

De hecho, GaN ha sido el heredero aparente del silicio en los amplificadores de potencia 5G durante años, especialmente cuando se trata de redes 5G MMW. Lo que lo hace tan atractivo es su capacidad para manejar de manera eficiente un voltaje más alto en un área mucho más pequeña que los dispositivos MOSFET de difusión lateral (LDMOS) comparables. Además, puede alimentar una gama mucho más amplia de frecuencias MMW que el silicio estándar. (Fogarty, 2019)

### Diseño de chips para la defensa

### Sistemas Integrados

Los sistemas electrónicos integrados los podemos definir como un conjunto de componentes electrónicos, normalmente en un único chip o en un SiP, que trabajan juntos de manera coordinada para realizar una función específica como, por ejemplo, controlar un equipo industrial, procesar señales o gestionar datos. En definitiva, es una solución tecnológica eficiente y optimizada que integra hardware y, a menudo, software para cumplir con una función electrónica determinada dentro de un equipo o producto.

Normalmente los sistemas electrónicos integrados necesitan captar datos, que suelen hacer mediante los sensores. Éstos captan señales del mundo físico, por lo que son, generalmente, magnitudes analógicas, que se transforman, por medio del sensor en señales eléctricas analógicas que se pasan a digitales mediante circuitos conocidos como "convertidores analógico-digitales", que son circuitos que realizan una función esencial y su diseño depende de varios factores como la precisión requerida por el sistema, la velocidad de conversión, el consumo de

energía, etc. Todos estos parámetros determinan el tipo de convertidor A/D utilizado. Una vez convertidos los parámetros físicos captados por los sensores en palabras de n bits, estos son procesados (DSP, microcontrolador, etc. y memorias). Mediante circuitos de comunicaciones se envían (y reciben) los resultados del procesado y se activan (si procede) los activadores (efecto). (ver figura 27)

# Entrada Analógica (datos) Captación de datos (Sense) Procesado (Think) Comunicaciones (Communicate)

### Estructura de los sistemas electrónicos integrados.

<u>Figura 27</u>. Sistemas integrados: Captación de datos (sensores), procesado(CPUs, GPUs, memorias,...), Actuadores y comunicaciones. Fuente: IPCEI-Microelectronics/CT Chapeau Text y Elaboración propia.

### Sensores en la Defensa

Uno de los puntos fundamentales para los sistemas de IA de computación en el borde es el suministro de datos, tanto para entrenamiento como para inferencia. El suministro de datos para inferencia en computación en el borde, por ejemplo, para un vehículo autónomo, o para un sistema de guiado de misiles, debe ser en tiempo real. Esta captación de datos, en tiempo real, lo realizan los sistemas de sensores. En este sentido, los sensores son elementos clave en el funcionamiento de los sistemas de defensa.

Uno de los dispositivos más esenciales en la industria de defensa es el sensor para capturar datos Las innovaciones en vigilancia, comunicación y transporte dependen de estos sensores simples para crear una observación de red intrincada. Las FFAA. utilizan, principalmente, los siguientes:

- Los sensores activos pueden localizar objetos en su vecindad mediante el uso de señales o longitudes de onda de luz. Se utilizan en navegación, defensa aérea, vigilancia, búsqueda y rescate y tecnología de sonar. A menudo utilizan una fuente de radiación interna para iluminar su entorno.

- <u>Los sensores portátiles</u> se pueden usar directamente en el cuerpo y transmitir datos tanto para entrenamiento como para fines del mundo real. Se pueden usar para rastrear soldados y mejorar las comunicaciones. Son compactos y duraderos para acomodar a un individuo en movimiento.

- <u>Los sensores de cámara</u> ayudan a detallar los cambios en el entorno y complementan los sistemas de vigilancia. Pueden ayudar a rastrear objetivos e identificar rostros o movimiento.

- <u>Los sensores MEMS</u> (sistemas microelectromecánicos) son un tipo de sensor que detecta los cambios de presión dentro de las aeronaves, acumula datos en satélites e identifica si los vehículos desconocidos son amigos o enemigos. Son compactos, fiables y rentables.

- Los sensores infrarrojos pueden ayudar a detectar distintos tipos de armas que pueden pasar desapercibidas a simple vista. Ciertas sustancias químicas y explosivos pueden resultar difíciles de detectar sin la ayuda de la tecnología infrarroja.

### Semiconductores y su uso en Defensa

Los semiconductores desempeñan un papel crucial en diversas aplicaciones militares, contribuyendo a los sistemas de comunicación, tecnologías de cifrado, sistemas de radar, guía de misiles y guerra electrónica. Su pequeño tamaño, bajo consumo de energía y alta confiabilidad los hacen ideales para tecnologías militares que requieren compacidad, eficiencia y durabilidad.

En los <u>sistemas de comunicación</u>, los semiconductores se utilizan en el desarrollo de radios avanzadas, comunicaciones por satélite e infraestructura de red. Permiten una transmisión de datos más rápida, una calidad de señal y una conectividad mejoradas.

Los semiconductores también desempeñan un papel vital en <u>las tecnologías de cifrado</u>, garantizando una comunicación segura y protegiendo la información militar confidencial del acceso no autorizado.

En los <u>sistemas de radar</u>, los semiconductores se utilizan en la creación de amplificadores de alta frecuencia y componentes de procesamiento de señales. Estos componentes permiten la detección y el seguimiento precisos de los objetivos, mejorando el conocimiento de la situación y ayudando en la identificación de amenazas.

Los semiconductores también se utilizan en la **guerra electrónica**, donde permiten la creación de contramedidas electrónicas para interrumpir las comunicaciones enemigas y los sistemas de radar. Los **sistemas de guía de misiles** basados en semiconductores utilizan sensores y procesadores para calcular las trayectorias de los objetivos y guiar los misiles hacia sus objetivos previstos con precisión y exactitud.

### Condiciones que deben cumplir los chips de Defensa

En el diseño de chips para defensa hay que tener en cuenta una serie de condiciones especiales debido a su utilización en ambientes hostiles, con dificultades de recambio y mantenimiento, estableciéndose un conjunto de especificaciones que estos chips deberán cumplir para ser certificados en grado militar.

### Rango de temperatura y tolerancia ambiental

- Temperatura de operación: -55 ºC a +125 ºC (algunas veces puede llegar hasta + 200 ºC)

- Resistencia a la radiación: Alta (rad-hard)

- Resistencia a golpes y vibraciones: Resiste condiciones extremas (Mil-STD 883)

- Resistencia a la humedad y a la corrosión: Protegido contra la humedad y la niebla salina.

### Confiabilidad y Longevidad

- Tasa de fallos: Muy baja (diseñada para sistemas de misión crítica)

- *Vida útil:* 15-30 años

- Estándares de prueba: MIL-STD-883 (pruebas de fiabilidad de estándar militar)

### Seguridad y Anti manipulación

- *Características Anti manipulación:* Arranque seguro, mecanismos de autodestrucción y de cifrado en hardware.

- Protección electromagnética (EMI/EMC): Protegido para evitar ataques electromagnéticos.

- **Seguridad de la cadena de suministro:** Seguimiento estricto, a menudo integrado en fábricas seguras.

### **Endurecimiento por Radiación (rad-hard)**

- Resistencia a la Radiación: Diseñado para soportar rayos gamma, rayos cósmicos y bombardeo de neutrones.

- Dosis ionizante total (TID) Tolerancia: 100 Krad- 1Mrad

### Proceso de fabricación y materiales

- Nodo tecnológico del proceso: Más grandes que los chips comerciales para robustez (90 nm, 120 nm, 180 nm).

- Material del sustrato: Silicio, SOI, SiC, GaN on SiC

- Encapsulado: Cerámico, sellado con metal.

Los chips militares evitan los nodos ultrapequeños (5 nm o menos) debido a la sensibilidad a la radiación, así como a la mayor robustez de los nodos más grandes.

### Costo y disponibilidad

- Costo: Cuestan entre 10 y 100 veces más que los chips comerciales equivalentes.

- Volumen de producción: Volumen bajo (Pedidos personalizados, fábricas clasificadas).

- *Disponibilidad:* Restringida, controlada por los gobiernos.

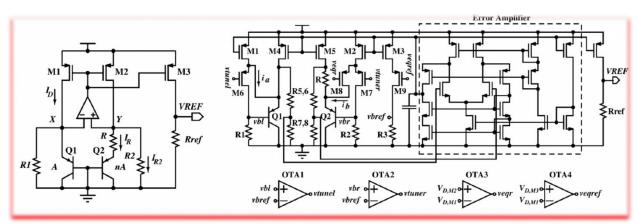

<u>Figura 28</u>. Generador de tensión de referencia: a ) el de la izquierda es para uso comercial; b) el de la derecha es un generador de tensión de referencia diseñado para cumplir con las especificaciones militares.

Como puede apreciarse en la figura 28 el diseño de un generador de tensión de referencia es mucho más complejo en el caso militar que en el caso comercial (circuito de la izquierda) para poder cumplir con los requerimientos de mayor estabilidad con una variación mayor de la temperatura (Rango militar) y la certificación MIL-STD.

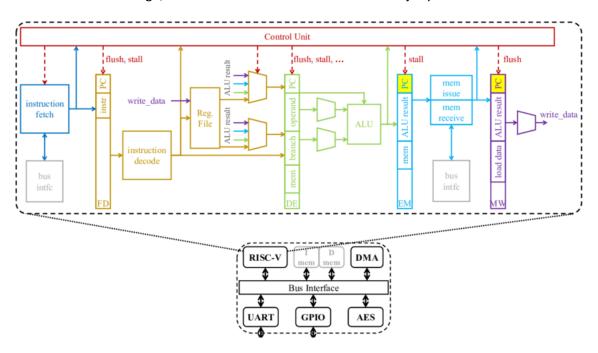

### **Hardware Abierto (RISC V)**

<u>RISC-V</u> es una arquitectura de conjunto de instrucciones (ISA) abierta y modular que ha ganado interés en aplicaciones de defensa por su flexibilidad y ausencia de restricciones de propiedad intelectual. Sin embargo, su uso en entornos militares tiene ventajas y desafíos.

<u>Figura 29</u>. Diagrama simplificado arquitectura RISC-V. Fuente: Kiaei,P & Schaumont, P., 2022, IACR transactions on Cryptographic hardware and Embedded Systems.

Ventajas de RISC-V para Defensa:

### 1. Soberanía Tecnológica y Reducción de Dependencia

• Al ser una arquitectura abierta, los gobiernos y empresas pueden desarrollar procesadores personalizados sin depender de empresas como Intel, AMD o ARM.

China y Rusia están invirtiendo en RISC-V para evitar sanciones y restricciones de exportación de chips avanzados.

### 2. Seguridad y Personalización

• Los procesadores RISC-V pueden diseñarse con medidas de seguridad específicas, como criptografía avanzada y protección contra ataques de hardware.

En efecto, en defensa, se pueden crear chips resistentes a ciberataques o adaptados a sistemas clasificados sin depender de proveedores extranjeros.

### 3. Eficiencia Energética y Bajo Consumo

• Su diseño permite optimizaciones en consumo energético, lo cual es clave para drones, satélites militares y dispositivos portátiles para soldados.

### 4. Escalabilidad y Modularidad

• RISC-V permite personalizar la arquitectura según las necesidades de defensa, desde procesadores de bajo consumo hasta chips de alto rendimiento para supercomputación militar.

### 5. Costos Reducidos

• Al no pagar licencias a ARM o x86, los costos de desarrollo pueden ser menores en el largo plazo, favoreciendo la adopción en equipos de defensa con grandes volúmenes de producción.

Inconvenientes de RISC-V para Defensa:

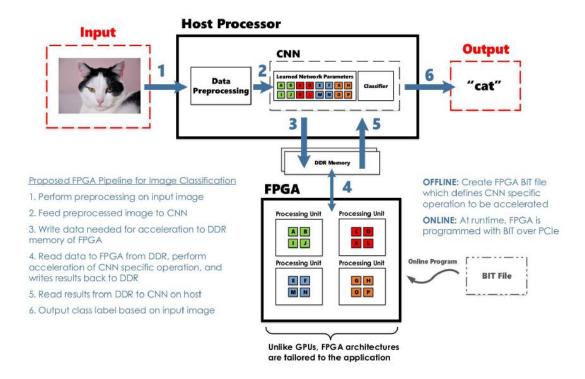

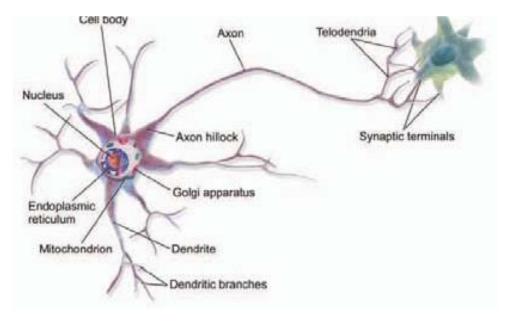

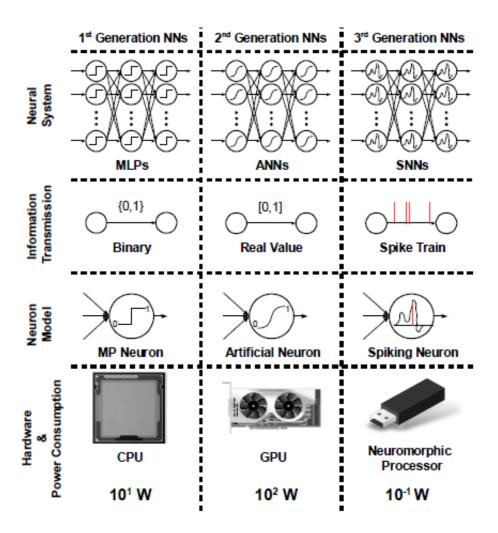

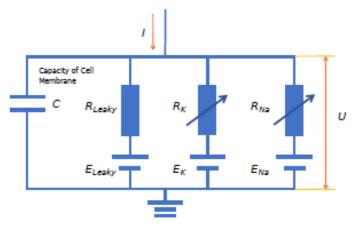

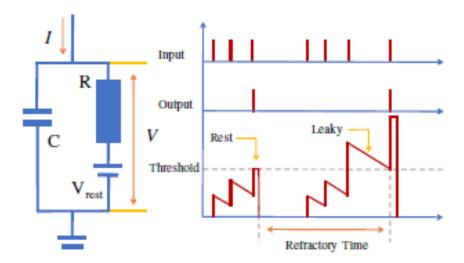

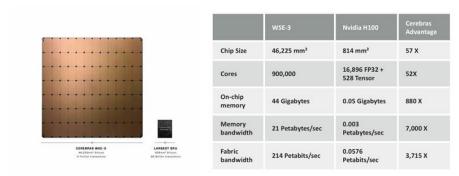

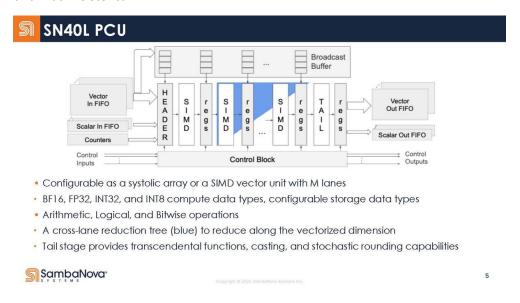

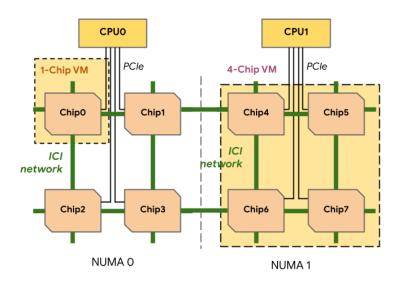

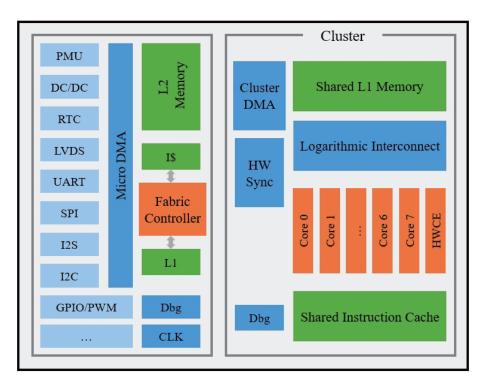

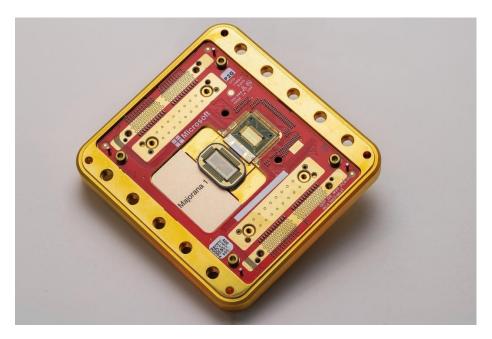

### 1. Ecosistema Inmaduro